計(jì)算機(jī)軟硬件協(xié)同創(chuàng)新 解析《計(jì)算機(jī)組織與設(shè)計(jì)的軟硬件接口》

計(jì)算機(jī)系統(tǒng)的高效運(yùn)行離不開軟硬件的緊密協(xié)作,《計(jì)算機(jī)組織與設(shè)計(jì)的軟硬件接口》一書為此提供了關(guān)鍵的理論基礎(chǔ)和實(shí)踐指導(dǎo)。軟硬件接口作為連接計(jì)算機(jī)硬件底層結(jié)構(gòu)與上層軟件應(yīng)用的橋梁,其設(shè)計(jì)與優(yōu)化直接決定了系統(tǒng)的性能、可靠性和能效。

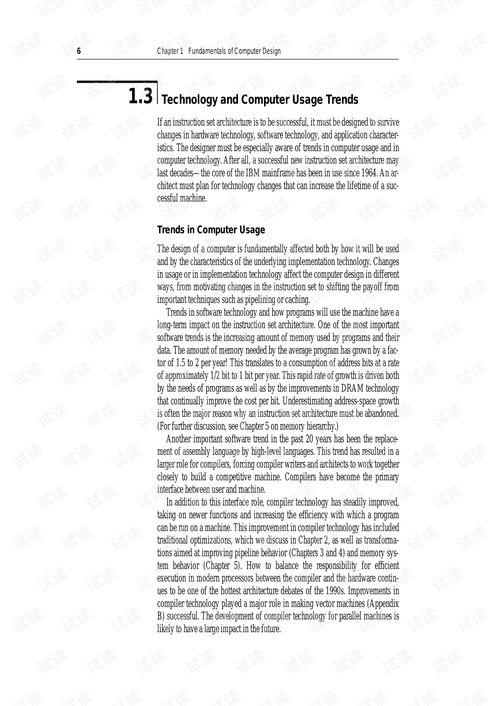

從硬件研發(fā)視角看,現(xiàn)代處理器架構(gòu)、內(nèi)存層次、總線設(shè)計(jì)等都需充分考慮軟件需求。例如,指令集架構(gòu)(ISA)的設(shè)計(jì)需平衡硬件實(shí)現(xiàn)復(fù)雜度與軟件編程便利性;緩存機(jī)制需適應(yīng)操作系統(tǒng)調(diào)度與應(yīng)用程序的數(shù)據(jù)訪問模式。硬件研發(fā)人員通過模擬、原型驗(yàn)證等方式,確保接口能夠高效支持操作系統(tǒng)、編譯器及各類應(yīng)用軟件。

軟件研發(fā)同樣依賴對硬件接口的深入理解。操作系統(tǒng)需管理硬件資源(如CPU時(shí)間片、內(nèi)存分頁),編譯器需將高級語言代碼轉(zhuǎn)換為可執(zhí)行指令,應(yīng)用程序則需利用硬件特性(如并行計(jì)算單元)提升性能。優(yōu)化軟件往往需針對特定硬件接口進(jìn)行調(diào)整,例如使用向量指令加速科學(xué)計(jì)算,或依據(jù)內(nèi)存延遲特性設(shè)計(jì)數(shù)據(jù)結(jié)構(gòu)。

當(dāng)前軟硬件研發(fā)正面臨新的挑戰(zhàn)與機(jī)遇。隨著人工智能、物聯(lián)網(wǎng)等技術(shù)的發(fā)展,異構(gòu)計(jì)算(如CPU、GPU、FPGA協(xié)同)成為趨勢,軟硬件接口需支持更靈活的資源配置。開源指令集(如RISC-V)的興起降低了硬件創(chuàng)新門檻,推動(dòng)軟硬件協(xié)同設(shè)計(jì)走向開放生態(tài)。安全需求促使接口設(shè)計(jì)加入權(quán)限隔離、加密機(jī)制等特性。

軟硬件研發(fā)將更注重跨層優(yōu)化。硬件設(shè)計(jì)需提前融入軟件工作負(fù)載分析,軟件開發(fā)則需適應(yīng)硬件動(dòng)態(tài)調(diào)節(jié)能力(如功耗管理)。《計(jì)算機(jī)組織與設(shè)計(jì)的軟硬件接口》所強(qiáng)調(diào)的系統(tǒng)性思維,將繼續(xù)引導(dǎo)研發(fā)者打破軟硬件邊界,構(gòu)建更智能、高效的計(jì)算平臺。

如若轉(zhuǎn)載,請注明出處:http://www.j2e7f76.cn/product/63.html

更新時(shí)間:2026-04-20 03:41:44